As AI workloads continue to surge and data centers struggle to keep pace with rising power demands, a new semiconductor startup is stepping into the spotlight with a bold promise to cut chip energy consumption in half. PowerLattice, founded in 2023 by former engineers from Qualcomm, NUVIA, and Intel, has emerged from stealth with a breakthrough chiplet and a powerful endorsement from one of the industry’s most influential figures.

On Monday, the company announced a $25 million Series A round led by Playground Global and Celesta Capital, pushing total funding to $31 million. Among the investors is former Intel CEO Pat Gelsinger, who now serves as a general partner at Playground Global.

A High-Profile Vote of Confidence

Gelsinger described PowerLattice’s work as a rare and highly technical effort to solve one of the semiconductor industry’s toughest challenges: delivering power more efficiently at the chip level. He called the engineering team “a dream team of power delivery,” emphasizing that very few groups are capable of working on problems this complex.

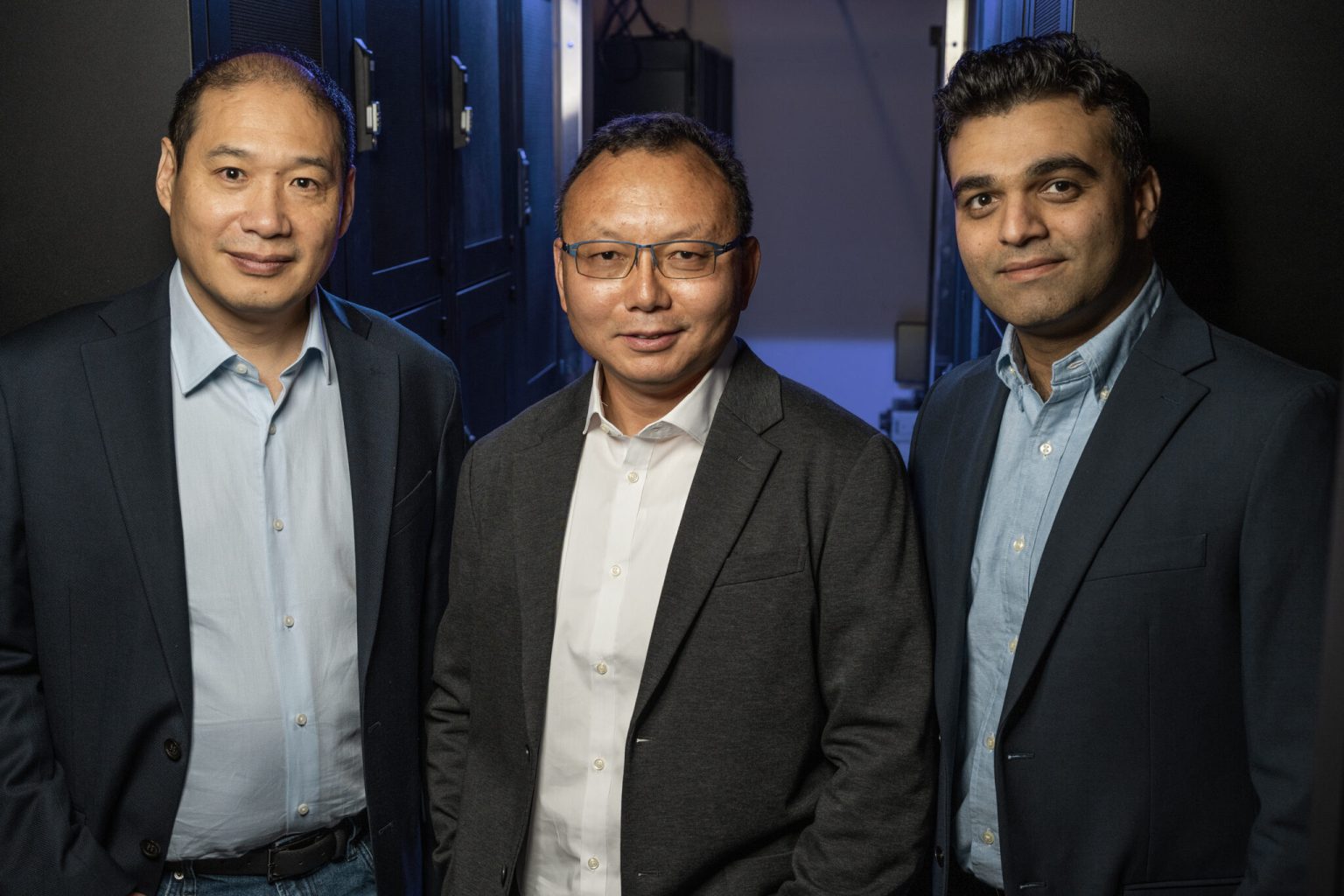

During PowerLattice’s initial pitch at Playground’s offices earlier this year, CEO Dr. Peng Zou and his team were visibly excited to meet Gelsinger, even asking for a selfie. But beyond the light moment, Gelsinger was struck by their technology and the potential impact it could have on future chip designs.

The startup’s innovation centers on a small power-delivery chiplet that brings energy significantly closer to the processor. By reducing the distance power must travel, the chiplet minimizes energy loss, delivering far greater efficiency than current solutions. While the concept sounds simple, engineering such a system is a formidable challenge, which makes PowerLattice’s claims even more notable.

Two years after its founding, PowerLattice has already reached a major development milestone. Its first batch of chiplets is now being produced by TSMC, the world’s leading chip manufacturer, with an unnamed customer currently testing the technology’s performance.

Testing Begins Ahead of Industry Rollout

PowerLattice expects to expand access to additional customers in the first half of 2026, a timeline that aligns with rising industry interest in energy-efficient chip architectures. Because power consumption is becoming a bottleneck for AI compute growth, the company’s potential customer base includes major players like Nvidia, Broadcom, and AMD, as well as AI-focused chipmakers such as Cerberus, Grok, d-Matrix, and NextSilicon.

Although most chipmakers maintain internal teams dedicated to power-efficiency improvements, Gelsinger believes PowerLattice’s approach offers something distinctly new. He predicts companies may adopt a blended strategy, combining traditional methods with PowerLattice’s chiplet, but expects the startup to secure meaningful market traction once broader testing begins.

PowerLattice is entering a competitive landscape, with rivals like Empower Semiconductor, which recently raised a $140 million Series D round. Yet Gelsinger maintains that PowerLattice’s reported 50% energy-efficiency gain is “extraordinary” and strong enough to attract significant attention.

With AI’s global power footprint growing rapidly, Gelsinger expects PowerLattice to raise larger funding rounds as it moves toward commercial production. “The idea is bold, the benefits are large,” he said, noting that other companies will likely attempt similar approaches. “But PowerLattice has taken an important early lead.”